Była era, w której komputery były tak gigantyczne, że aby je zainstalować, z łatwością wymagało miejsca w pokoju. Ale dziś są tak rozwinięte, że możemy je łatwo nosić nawet jako zeszyty. Innowacją, która to umożliwiła, była koncepcja układów scalonych. W Obwody scalone , duża liczba aktywnych i elementy pasywne wraz z ich wzajemnymi połączeniami są rozwijane na małej krzemowej płytce, zwykle o przekroju 50 na 50 milicali. Podstawowe procesy stosowane przy produkcji takich obwodów obejmują wzrost epitaksjalny, zamaskowaną dyfuzję zanieczyszczeń, wzrost tlenków i wytrawianie tlenków, z wykorzystaniem fotolitografii do tworzenia wzorów.

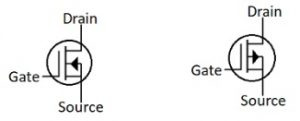

Elementy znajdujące się na płytce obejmują rezystory, tranzystory, diody, kondensatory itp. Najbardziej skomplikowanym elementem do wyprodukowania na układach scalonych są tranzystory. Tranzystory są różnych typów takie jak CMOS, BJT, FET. Na podstawie wymagań wybieramy rodzaj technologii tranzystorowej, która ma zostać wdrożona w układzie scalonym. W tym artykule zapoznajmy się z pojęciem Produkcja CMOS (lub) wytwarzanie tranzystorów jako CMOS.

Produkcja CMOS

Mniejsze zapotrzebowanie na straty mocy Technologia CMOS służy do implementacji tranzystorów. Jeśli potrzebujemy szybszego obwodu, tranzystory są realizowane IC przy użyciu BJT . Produkcja Tranzystory CMOS ponieważ układy scalone można wykonać trzema różnymi metodami.

Technologia N-well / P-well, w której dyfuzja typu n jest wykonywana na podłożu typu p lub dyfuzja typu p jest wykonywana odpowiednio na podłożu typu n.

Plik Technologia Twin Well , gdzie NMOS i tranzystor PMOS są rozwijane na płytce przez jednoczesną dyfuzję na epitaksjalnej podstawie wzrostu, a nie na podłożu.

Proces „Silicon On Insulator”, w którym zamiast stosowania krzemu jako podłoża stosuje się materiał izolacyjny w celu zwiększenia szybkości i podatności na zatrzaskiwanie.

Technologia N-well / P-well

CMOS można uzyskać integrując oba Tranzystory NMOS i PMOS na tej samej płytce silikonowej. W technologii N-well studnia typu n jest dyfundowana na podłożu typu p, podczas gdy w P-well jest odwrotnie.

Kroki produkcji CMOS

Plik Proces produkcji CMOS pływ jest wykonywana przy użyciu dwudziestu podstawowych etapów produkcji, a wytwarzana w technologii N-well / P-well.

Wykonanie CMOS dobrze przy użyciu N.

Krok 1: Najpierw wybieramy podłoże jako podstawę do produkcji. W przypadku N-dołka wybiera się podłoże silikonowe typu P.

Podłoże

Krok 2 - Utlenianie: Selektywna dyfuzja zanieczyszczeń typu n odbywa się przy użyciu SiO2 jako bariery chroniącej fragmenty wafla przed zanieczyszczeniem podłoża. SiOdwajest układany w procesie utleniania przeprowadzanym przez wystawienie podłoża na działanie wysokiej jakości tlenu i wodoru w komorze utleniającej w temperaturze około 1000 ° C0do

Utlenianie

Krok 3 - Uprawa fotorezystu: Na tym etapie, aby umożliwić selektywne trawienie, warstwa SiO2 jest poddawana procesowi fotolitografii. W tym procesie wafel jest powlekany jednorodną warstwą fotoczułej emulsji.

Uprawa Photoresist

Krok 4 - Maskowanie: Ten krok jest kontynuacją procesu fotolitografii. Na tym etapie za pomocą szablonu tworzy się pożądany wzór otwartości. Szablon ten służy jako maska na fotorezyst. Podłoże jest teraz wystawione na działanie Promienie UV fotorezyst znajdujący się pod odsłoniętymi obszarami maski ulega polimeryzacji.

Maskowanie fotorezystu

Krok 5 - Usuwanie nienaświetlonego fotorezystu: Maskę usuwa się, a nienaświetlony obszar fotorezystu rozpuszcza się, wywołując wafel przy użyciu substancji chemicznej, takiej jak trójchloroetylen.

Usuwanie fotorezystu

Krok 6 - Wytrawianie: Płytka zanurzona jest w trawiącym roztworze kwasu fluorowodorowego, który usuwa tlenek z obszarów, przez które mają być dyfundowane domieszki.

Wytrawianie SiO2

Krok 7 - Usuwanie całej warstwy fotorezystu: Podczas proces wytrawiania nie ma to wpływu na te części SiO2, które są chronione przez warstwę fotorezystu. Maskę fotorezystu zdejmuje się teraz rozpuszczalnikiem chemicznym (gorący H2SO4).

Usunięcie warstwy fotorezystu

Krok 8 - Tworzenie N-dołka: Zanieczyszczenia typu n są dyfundowane do podłoża typu p przez odsłonięty obszar, tworząc w ten sposób zagłębienie N.

Powstanie N-dobrze

Krok 9 - Usuwanie SiO2: Warstwę SiO2 usuwa się teraz za pomocą kwasu fluorowodorowego.

Usuwanie SiO2

Krok 10 - Osadzanie polikrzemu: Niewspółosiowość bramy a Tranzystor CMOS doprowadziłoby do niepożądanej pojemności, która mogłaby uszkodzić obwód. Dlatego też, aby zapobiec temu „samoustawiającemu się procesowi bramki”, preferowane jest, gdy obszary bramek są tworzone przed utworzeniem źródła i drenu za pomocą implantacji jonów.

Osadzanie polikrzemu

Do formowania przewężki używany jest polikrzem, ponieważ wytrzymuje on wysoką temperaturę powyżej 80000c gdy wafel poddaje się wyżarzaniu w celu utworzenia źródła i drenu. Polikrzem jest osadzany za pomocą Proces osadzania chemicznego na cienką warstwę tlenku bramy. Ten cienki tlenek bramki pod warstwą polikrzemu zapobiega dalszemu domieszkowaniu pod obszarem bramki.

Krok 11 - Utworzenie regionu bramnego: Z wyjątkiem dwóch regionów wymaganych do utworzenia bramy dla Tranzystory NMOS i PMOS pozostała część polikrzemu jest usuwana.

Utworzenie regionu bramnego

Krok 12 - Proces utleniania: Warstwa utleniania jest osadzona na waflu, który działa jak tarcza dla dalszego procesy dyfuzji i metalizacji .

Proces utleniania

Krok 13 - Maskowanie i dyfuzja: W celu wykonania obszarów dyfuzji zanieczyszczeń typu n metodą maskowania wykonuje się małe szczeliny.

Maskowanie

Wykorzystując proces dyfuzji, opracowuje się trzy regiony n + do tworzenia końcówek NMOS.

Dyfuzja azotu

Krok 14 - Usuwanie tlenku: Warstwa tlenku zostaje zdjęta.

Usuwanie tlenku

Krok 15 - Dyfuzja typu P: Podobnie jak w przypadku dyfuzji typu n, do formowania wyprowadzeń PMOS typu p, dyfuzja jest wykonywana.

Dyfuzja typu P.

Krok 16 - Układanie grubego pola tlenku: Przed utworzeniem metalowych końcówek układa się gruby tlenek pola, aby utworzyć warstwę ochronną dla obszarów płytki, w których nie są wymagane żadne końcówki.

Gruba warstwa tlenku pola

Krok 17 - Metalizacja: Ten krok jest używany do tworzenia metalowych zacisków, które mogą zapewnić połączenia. Aluminium jest rozprowadzone na całej płytce.

Metalizacja

Krok 18 - Usuwanie nadmiaru metalu: Nadmiar metalu jest usuwany z wafla.

Krok 19 - Tworzenie terminali: W szczelinach powstałych po usunięciu nadmiaru metalowych końcówek są utworzone dla połączeń wzajemnych.

Tworzenie terminali

Krok 20 - Przypisywanie nazw terminali: Nazwy są przypisywane do terminali Tranzystory NMOS i PMOS .

Przypisywanie nazw terminali

Wykonywanie CMOS przy użyciu technologii P well

Proces p-well jest podobny do procesu N well z wyjątkiem tego, że tutaj stosuje się podłoże typu n i przeprowadza się dyfuzje typu p. Dla uproszczenia zwykle preferowany jest proces N-well.

Produkcja CMOS z podwójną rurką

Stosując proces dwururowy można sterować wzmocnieniem urządzeń typu P i N. Różne kroki związane z wytwarzanie CMOS metodą dwururową są następujące

- Pobiera się lekko domieszkowane podłoże typu n lub p i stosuje się warstwę epitaksjalną. Warstwa epitaksjalna zabezpiecza problem zatrzaskiwania chipa.

- Hoduje się warstwy krzemu o wysokiej czystości o zmierzonej grubości i dokładnym stężeniu domieszki.

- Tworzenie rur do studni P i N.

- Cienka konstrukcja tlenkowa dla ochrony przed zanieczyszczeniami podczas procesów dyfuzji.

- Źródło i dren są tworzone za pomocą metod implantacji jonów.

- Wykonane są nacięcia na części do metalowych styków.

- Metalizacja jest wykonywana w celu rysowania metalowych styków

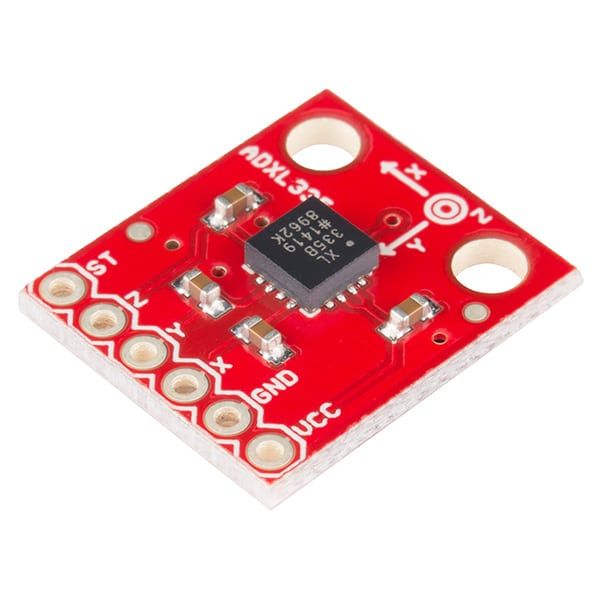

Układ CMOS IC

Widok z góry do CMOS produkcja i układ jest podawany. Tutaj można wyraźnie zobaczyć różne metalowe styki i dyfuzje w N.

Układ CMOS IC

A więc o to chodzi Techniki wytwarzania CMOS . Rozważmy 1-w-kwadratowy wafel podzielony na 400 żetonów o powierzchni 50 mil na 50 milicali. Wytworzenie tranzystora zajmuje obszar 50 mil2. Stąd każdy układ scalony zawiera 2 tranzystory, więc na każdej płytce są zbudowane tranzystory 2 x 400 = 800. Jeśli w każdej partii przetwarzanych jest 10 płytek, można jednocześnie wyprodukować 8000 tranzystorów. Jakie różne elementy zaobserwowałeś w układzie scalonym?